As the electronics industry approaches the limits of packing density on computer chips, Chip producers must focus on building quality rather than quantity.

The industry is shifting its focus from miniaturizing individual transistors on a single layer to vertically stacking multiple layers of transistors and semiconductor components, effectively transforming traditional chip architecture into a high-rise structure. These sophisticated multi-layered chips have the potential to process exponentially more complex data and execute numerous advanced functions far surpassing the capabilities of today’s electronic devices.

While significant progress has been made in recent years, a major obstacle remains: the platform upon which microchips are fabricated. As we converse, intricate silicon substrates serve as the fundamental foundation for cultivating high-quality, single-crystal semiconductor materials. Innovative chip designs rely on the strategic incorporation of thick silicon substrates across each layer, thereby introducing deliberate latency in data transmission between functionally distinct semiconductor layers.

MIT engineers have overcome this challenge by developing a multi-layered chip design that eliminates the need for silicon wafer substrates, operating efficiently at low temperatures that safeguard the underlying circuitry’s integrity.

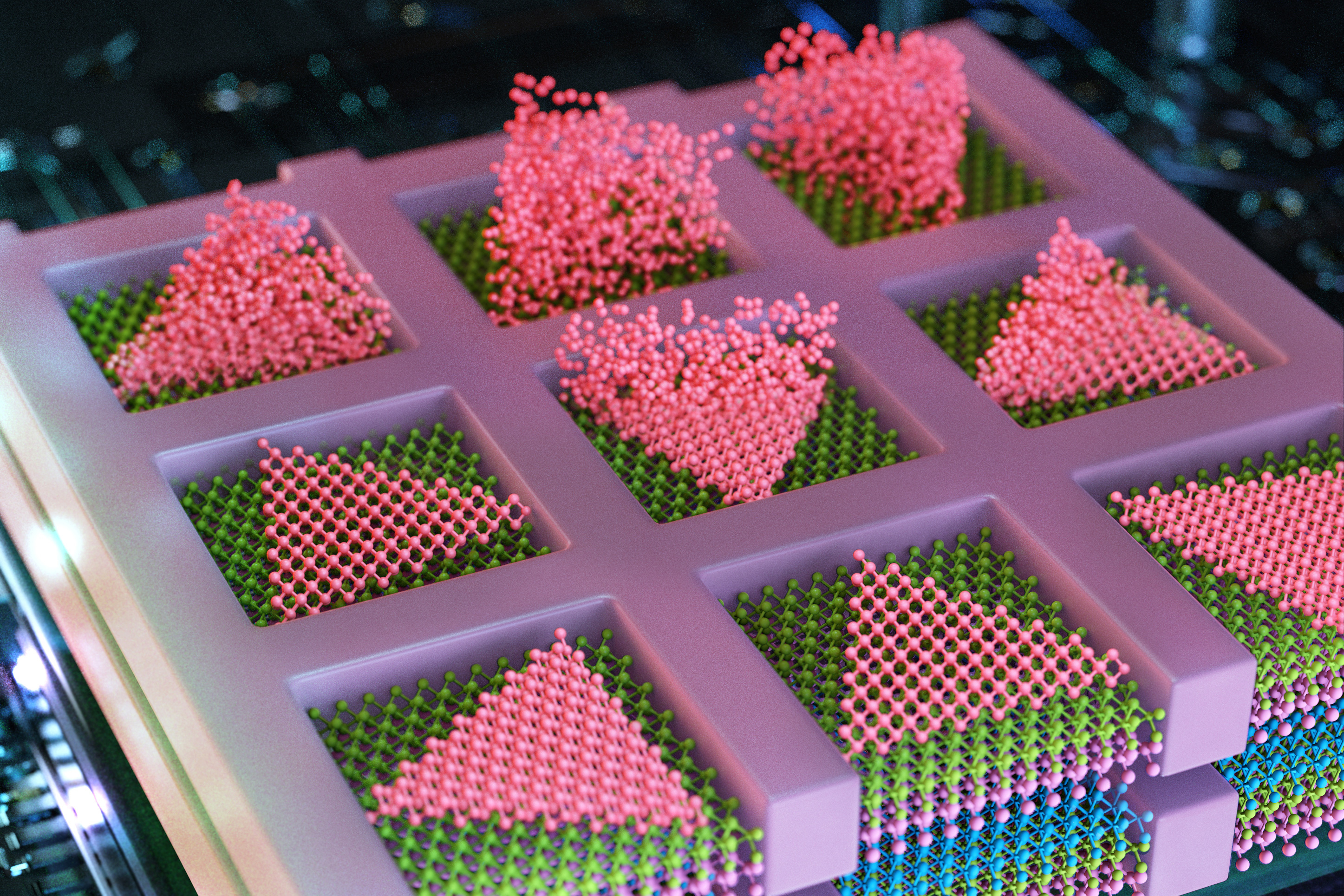

Researchers employed a novel approach to fabricate a multilayered chip, featuring alternating layers of high-purity semiconductor materials grown directly atop one another.

The innovative approach enables engineers to fabricate high-performing transistors, memory, and logic components on any arbitrary crystalline surface, transcending the traditional constraint of silicon wafer substrates. Without these thick silicon substrates, multiple semiconducting layers can come into direct contact, leading to faster and more efficient communication and computation between layers, according to the researchers.

Researchers propose harnessing this innovation to fabricate AI hardware resembling stacked chips for laptops or wearables, capable of rivalling today’s supercomputers in speed and efficiency while storing vast amounts of data comparable to physical data centres.

“According to research author and MIT affiliate professor of mechanical engineering Jeehwan Kim, this groundbreaking discovery has far-reaching implications for the semiconductor industry, enabling the creation of stacked chips unhindered by traditional constraints.” “This could lead to substantial improvements in computing efficiency, with potential applications in AI, logical processing, and memory enhancement.”

The research’s MIT co-authors, led by first author Ki Seok Kim, include Seunghwan Oh, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Park, Jin Feng, and Sangho Lee. They collaborated with researchers from Samsung Superior Institute of Technology, Sungkyunkwan University in South Korea, and the University of Texas at Dallas.

Researchers in Kim’s group announced a breakthrough in 2023, successfully creating high-quality semiconductors on amorphous surfaces akin to the complex topographies found on finished integrated circuits. Researchers cultivated a novel type of two-dimensional material, specifically transition-metal dichalcogenides (TMDs), which holds great potential as a successor to silicon in the fabrication of tiny, high-functioning transistors. While traditional 2D materials maintain their semiconductor properties down to the atomic scale, silicon’s efficiency is significantly compromised by similar dimensional reductions.

The research team successfully cultivated transition metal dichalcogenides (TMDs) on silicon wafers with amorphous coatings, expanding their repertoire of TMDs beyond previous accomplishments. To coax atoms into rearranging themselves into high-quality single-crystalline form, rather than settling for random polycrystalline defects, Kim and his colleagues initially deposited a thin film, or “masks,” of silicon dioxide onto a silicon wafer, carefully patterning it with tiny openings, or pockets. Scientists subsequently poured a gas of atoms onto the masks, discovering that these atoms coalesced into “seed” structures within the microscopic pockets. The precise confinement allowed the seeds to grow uniformly, forming single-crystalline patterns in harmony.

At that point in time, the tactic struggled to function effectively at temperatures around 900 degrees Celsius.

“You’ll need to fabricate these single-crystal materials at temperatures below 400 degrees Celsius; otherwise, the underlying circuitry will be irreparably damaged,” Kim explains. “So, our assignment was to conduct an analogous analysis at temperatures below 400 degrees Celsius.” If allowed to happen, the impact would be considerable.

Researchers considered refining their approach to grow high-quality, two-dimensional materials at temperatures so low they wouldn’t compromise underlying electronics. In the realm of metallurgy, scientists found a refreshingly simple solution. As metallurgists pour molten metal into a mold, the liquid gradually nucleates, forming crystals that coalesce into a uniform, patterned structure that eventually solidifies into a robust form. Researchers have found that nucleation occurs with greatest efficiency when liquid metal is introduced to the edges of mild steel, serving as a conducive site for precipitation to take place.

“It’s widely acknowledged that nucleation on edge defects typically demands significantly less energy – and heat,” Kim notes. “We leveraged insights from metallurgy to optimize our approach to developing cutting-edge AI hardware for the future.”

The team aimed to grow single-crystalline transition metal dichalcogenides (TMDs) onto a pre-fabricated silicon wafer featuring transistor circuitry. Initially, they covered the circuitry with a layer of silicon dioxide, leveraging their prior research in this area. Researchers found that by depositing “seeds” of TMD on the edges of mask pockets, they could grow single-crystalline materials at relatively low temperatures of 380°C, whereas seeds placed in the pocket’s center required higher temperatures to achieve this crystal structure.

Researchers took their innovative approach to create a multilayered chip featuring alternating layers of two distinct transition metal dichalcogenides (TMDs): molybdenum disulfide, a prime candidate for n-type transistor fabrication; and tungsten diselenide, a material with potential for p-type transistor production. Each p- and n-type transistor serves as a fundamental building block for executing any logic operation in digital design. The crew demonstrated the capability to grow individual supplies into single-crystalline form, layering them seamlessly atop one another without necessitating intermediate silicon wafers. Kim asserts that this approach will effectively quadruple the density of a chip’s semiconducting components, particularly metal-oxide semiconductor (MOS) structures, which are crucial building blocks in modern logic circuits.

“A product resulting from our method should not only comprise a 3D logic chip, but also 3D memory and their combinations,” Kim notes. “With our innovative monolithic 3D approach, you can design and stack hundreds of logic and memory layers, allowing them to seamlessly communicate.”

“Traditionally, 3D chips have been manufactured using silicon wafers with drilled holes between them, a process that constrains the number of stacked layers, vertical alignment decisions, and yields.” “Our growth-oriented approach swiftly resolves all concerns.”

Kim has recently spun off a new company, FS2, to further commercialize their innovative stackable chip design.

“We currently present a concept for a compact device array,” he states. “The next milestone is developing AI chips that operate at the same level of sophistication as current state-of-the-art capabilities.”

This analysis is substantiated, in part, by Samsung’s Superior Institute of Expertise and the U.S. The Air Force Office of Scientific Research.